# ADIODA-PCI12

EDV-Nr.: A-403400

8 A/D-Eingänge 12 Bit 1 D/A-Ausgang 12 Bit 24 TTL-Ein-/Ausgänge 3 \* 16-Bit-Zähler - interruptfähig

# Copyright® 2006 by Messcomp Datentechnik GmbH

Diese Dokumentation ist urheberrechtlich geschützt. Alle Rechte sind vorbehalten.

Messcomp Datentechnik GmbH behält sich das Recht vor, die in dieser Dokumentation beschriebenen Produkte jederzeit und ohne Vorankündigung zu verändern.

Ohne schriftliche Genehmigung der Firma Messcomp Datentechnik GmbH darf diese Dokumentation in keinerlei Form vervielfältigt werden.

#### Geschützte Warenzeichen

IBM PC, PC/XT und PC/AT sind geschützte Warenzeichen von International Business Machines (IBM).

BASIC ist ein geschütztes Warenzeichen von Dartmouth College. Turbo Pascal, Turbo C sind geschützte Warenzeichen von Borland. Quickbasic ist ein eingetragenes Warenzeichen von Microsoft. Powerbasic ist ein eingetragenes Warenzeichen von Robert S. Zale.

wasco® ist ein eingetragenes Warenzeichen.

#### Haftungsbeschränkung

Die Firma Messcomp Datentechnik GmbH haftet für keinerlei, durch den Gebrauch der Interfacekarte ADIODA-PCI12<sub>LAP</sub> und dieser Dokumentation, direkt oder indirekt entstandenen Schäden.

# Inhaltsverzeichnis

# 1. Produktbeschreibung

#### 2. Installation der ADIODA-PCI12LAP

2.1 Installation der Karte in den Rechner

#### 3. Anschlussstecker

- 3.1 Lage der Anschlussstecker auf der Platine

- 3.2 Steckerbelegung von P1

- 3.3 Steckerbelegung von P9

- 3.4 Steckerbelegung von P9 auf D-Sub37 (Steckerverlegungsset)

#### 4. Jumperblöcke

- 4.1 Lage der Jumperblöcke auf der Platine

- 4.2 Jumperblockbelegung JP1

- 4.3 Jumperblockbelegung JP2

- 4.4 Jumperblockbelegung JP3

- 4.5 Jumperblockbelegung JP7

- 4.6 Jumperblockbelegung JP9

#### 5. Systemkomponenten

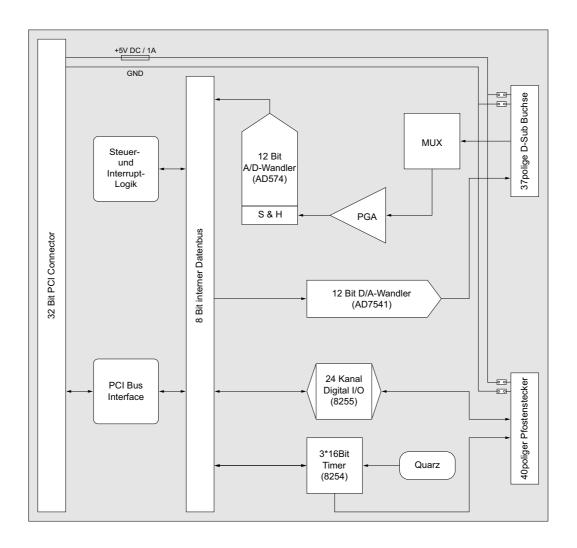

- 5.1 Blockschaltbild

- 5.2 Zugriff auf die Systemkomponenten

#### 6. 8 A/D-Eingänge 12 Bit

- 6.1 A/D-Kontrollregister

- 6.2 Multiplexer-Kanalauswahl

- 6.3 PGA-Verstärkungswahl

- 6.4 A/D-Betriebsarten (Modusbyte)

- 6.5 Abgleich A/D-Wandler und PGA

# 7. 1 D/A-Ausgang 12 Bit

- 7.1 Auswahl der Betriebsart und der Hauptreferenzspannung

- 7.2 Abgleich des D/A-Kanals

- 7.3 Programmierung des D/A-Kanals

# 8. 24 TTL Ein-/Ausgänge (8255)

# 9. 3 \* 16 Bit Zähler (Timer 8254)

## 10. Interrupt

- 10.1 Interrupt-Anforderungen

- 10.2 Interruptauslösung durch Statussignal des A/D-Wandlers (STS)

- 10.3 Interruptauslösung durch Timersignal

- 10.4 Interruptauslösung durch externes Signal

# 11. Programmierung unter DOS®

- 11.1 Programmierung der ADIODA-PCI12

- 11.2 Zuordnung der Portadressen

# 12. Programmierung unter Windows®

- 12.1 Programmierung der ADIODA-PCI12

- 12.2 Installation der Windows® Treiber

#### 13. Zubehör

- 13.1 Passendes wasco®-Zubehör

- 13.2 Anschlusstechnik (Anwendungsbeispiele)

- 13.3 Einzelkomponenten zur Eigenkonfektionierung

- 14. Fehlersuche

- 15. Technische Daten

- 16. Produkthaftungsgesetz

## 17. EG-Konformitätserklärung

#### Anhang

Programmierbarer Timer-Baustein 8254 Programmierbarer I/O-Baustein 8255

# 1. Produktbeschreibung

Die ADIODA-PCI12<sub>LAP</sub> verfügt über acht gemultiplexte massebezogene 12 Bit A/D-Eingangskanäle mit programmierbarem Verstärker und einer maximalen Summenabtastrate von 25 kS/s. Der Eingangsspannungsbereich (unipolar: 0..10 V, bipolar: +/-5 V, +/-10 V) wird mittels Jumper festgelegt. Der analoge Ausgangskanal wird durch einen multiplizierenden 12 Bit Digital/Analogwandler erreicht und ist ebenfalls mittels Jumper auf unipolare oder bipolare Betriebsart einstellbar. Interruptauslösungen sind durch den Timer oder durch das STS-Signal des A/D-Wandlers möglich. Außerdem verfügt diese Interfacekarte über einen programmierbaren digitalen Ein/Ausgabe-Baustein, einen Timer, einen Quarzoszillator und einen leistungsfähigen DC/DC-Wandler. Die A/D-Eingänge und der D/A-Ausgang sind der 37poligen D-Sub-Buchse am Slotblech der Platine, die TTL-Ein/Ausgänge und Timersignale einem 40poligen Pfostenstecker auf der Platine zugeführt. Die Signalverlegung auf eine 37polige D-Sub-Buchse mit Slotblech ist über ein optionales Steckerverlegungs-Set möglich. Die Belegungen aller Anschlussstecker der ADIODA-PCI12LAP sind identisch zu der ISA-Bus-Karte ADIODA-12 AP.

# 2. Installation der ADIODA-PCI12LAP

#### 2.1 Installation der Karte in den Rechner

Achten Sie vor dem Einbau der ADIODA-PCI12 darauf, dass der Rechner vom Netz getrennt oder zumindest ausgeschaltet ist. Beim Einbau der Interface-Karte in den laufenden Rechner besteht die Gefahr, dass neben der ADIODA-PCI12 auch andere Karten des PCs oder Rechners beschädigt oder zerstört werden.

Wählen Sie in Ihrem Rechner einen freien PCI-Steckplatz in den Sie dann die Karte einsetzen. Nehmen Sie dazu auch das Benutzerhandbuch Ihres Computers zu Hilfe. Verschrauben Sie das Slotblech der Platine mit dem Rechnergehäuse, damit sich die Karte nicht während des Betriebs unter Einwirkung der Anschlußkabel aus dem Steckplatz lösen kann.

# 3. Anschlussstecker

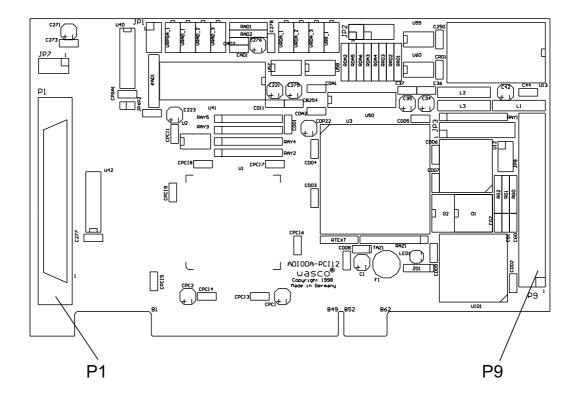

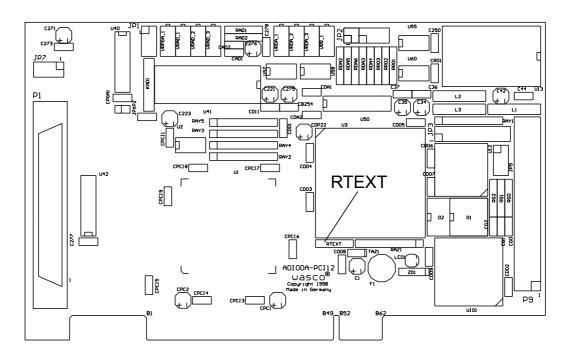

# 3.1 Lage der Anschlussstecker auf der Platine

P1: A/D-Eingangskanäle 0...7, Signale für externe Triggerung,

D/A-Ausgang

P9: 24 TTL Ein-/Ausgänge, Timersignale

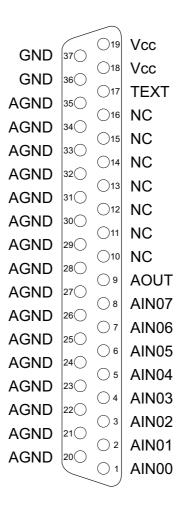

# 3.2 Steckerbelegung von P1

#### Vcc:

Interne Versorgungsspannung (+ 5V) des Rechners. Hier niemals eine externe Spannung anlegen.

# GND:

Masse des Rechners

#### NC:

Pin nicht belegt

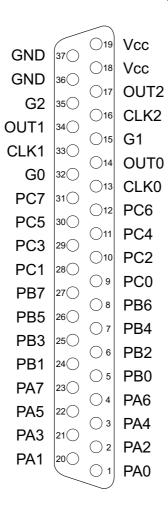

# 3.3 Steckerbelegung von P9

| NC   | 40 🔾 | <b>39</b>   | NC   |

|------|------|-------------|------|

| NC   | 38   | <b>37</b>   | Vcc  |

| GND  | 36 🔾 | <b>35</b>   | Vcc  |

| GND  | 34 🔾 | <b>○33</b>  | OUT2 |

| G2   | 32 🔾 | <b>31</b>   | CLK2 |

| OUT1 | 30 🔾 | <u></u>     | G1   |

| CLK1 | 28 🔾 | <u></u>     | OUT0 |

| G0   | 26 🔾 | <u></u>     | CLK0 |

| PC7  | 24 🔾 | <b>O</b> 23 | PC6  |

| PC5  | 22 🔾 | <b>O</b> 21 | PC4  |

| PC3  | 20 🔾 | <u></u> 19  | PC2  |

| PC1  | 18 🔾 | <u></u>     | PC0  |

| PB7  | 16 🔾 | <u></u>     | PB6  |

| PB5  | 14 🔾 | <u></u>     | PB4  |

| PB3  | 12 🔾 | <u></u>     | PB2  |

| PB1  | 10 🔾 | O 9         | PB0  |

| PA7  | 8 🔾  | O 7         | PA6  |

| PA5  | 6 🔾  | O 5         | PA4  |

| PA3  | 4 🔾  | Оз          | PA2  |

| PA1  | 2 🔾  | O 1         | PA0  |

|      | 1    |             |      |

#### Vcc:

Interne Versorgungsspannung (+ 5V) des Rechners. Hier niemals eine externe Spannung anlegen.

#### GND:

Masse des Rechners

## NC:

Pin nicht belegt

# 3.4 Steckerbelegung von P9 auf D-Sub 37 (Steckerverlegungsset)

#### Vcc:

Interne Versorgungsspannung (+ 5V) des Rechners. Hier niemals eine externe Spannung anlegen.

#### **GND**:

Masse des Rechners

# 4. Jumperblöcke

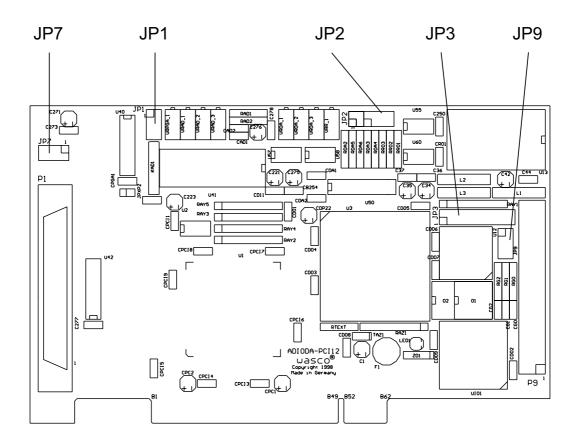

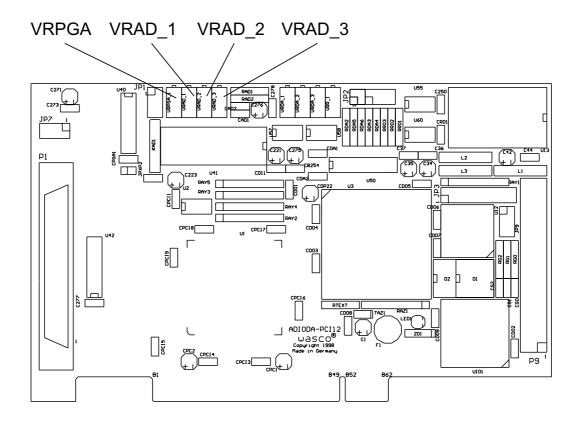

# 4.1 Lage der Jumperblöcke auf der Platine

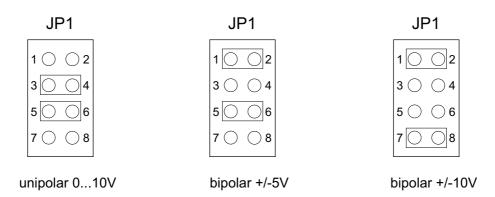

- JP1: Auswahl des A/D-Eingangsspannungsbereiches

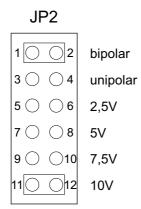

- JP2: Auswahl der Referenzspannung D/A-Ausgang

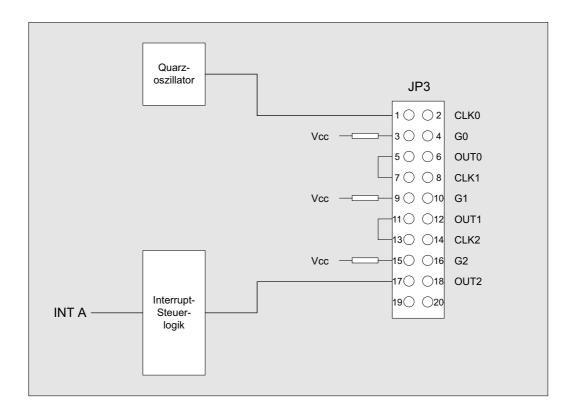

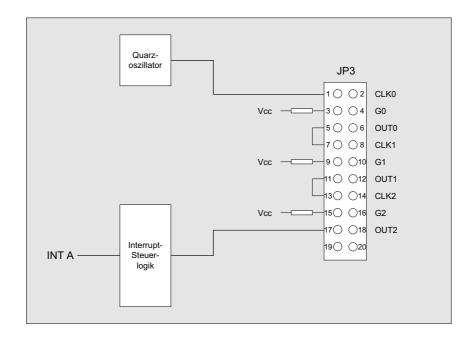

- JP3: Jumperblock für Anwendung des Timers

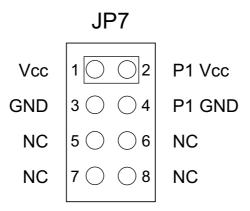

- JP7: Verbinden der internen Versorgungsspannung des PC auf die

- D-Sub Buchse P1

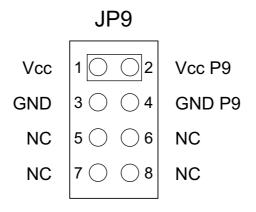

- JP9: Verbinden der internen Versorgungsspannung des PC auf den

- Pfostenstecker P9

# 4.2 Jumperblockbelegung JP1

Die Festlegung des A/D-Eingangsspannungsbereiches erfolgt über die Jumperstellung an JP1. Für die möglichen Eingangsspannungsbereiche ergeben sich folgende Jumperstellungen:

unipolare Betriebsart 0...10V

JP1

| 1 |            | <u> </u> |

|---|------------|----------|

| 3 |            | <u></u>  |

| 5 |            | 6        |

| 7 | $\bigcirc$ | <b>8</b> |

|   |            |          |

bipolare Betriebsart +/-5V

JP1

# bipolare Betriebsart +/-10V

# **Wichtiger Hinweis:**

Eingangsspannungen außerhalb des eingestellten Eingangsspannungsbereiches sowie Jumperstellungen, die von den hier genannten abweichen, sind um Beschädigungen an der ADIODA-PCI12<sub>LAP</sub> auszuschließen, unbedingt zu vermeiden.

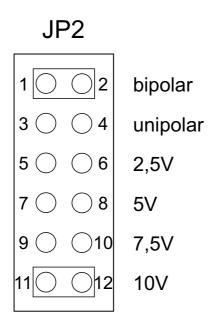

# 4.3 Jumperblockbelegung JP2

Durch Setzen zweier Jumper am Jumperblock JP2 können Sie die für Sie geeignete Hauptreferenzspannung  $V_{\text{Ref0}}$  sowie die Betriebsart (unipolar/bipolar) für den D/A-Ausgang auswählen. Standardmäßig werden vor der Auslieferung an JP2 die Jumperverbindungen 1-2 und 11-12 für  $V_{\text{Ref0}}$  = bipolar 10V gesetzt. Die Zuordnung der Betriebsart und der Spannungswerte für  $V_{\text{Ref0}}$  zu den Jumperverbindungen entnehmen Sie bitte den folgenden Beispielen.

Default Einstellung bei Auslieferung:

In dieser Einstellung wird der D/A-Ausgang im bipolaren Betrieb bei V<sub>Ref0</sub> = 10V betrieben.

In diesem Beispiel wird der D/A-Ausgang im unipolaren Betrieb bei V<sub>Ref0</sub> = 5V betrieben.

| JP2       |          |

|-----------|----------|

| 1 🔾 🔾 2   | bipolar  |

| 3 0 04    | unipolar |

| 5 0 6     | 2,5V     |

| 7 0 8     | 5V       |

| 9 🔾 🔾 10  | 7,5V     |

| 11 🔾 🔾 12 | 10V      |

|           |          |

# 4.4 Jumperblockbelegung JP3

#### Bitte beachten Sie:

Die Anschlüsse des Zählerbausteins 8254 sind dem Pfostenstecker P9 zugeführt, damit der Timer extern benutzt werden kann. Bei externer Zufuhr von Signalen an den Timer, müssen die entsprechenden Jumper entfernt werden. Jumper 19/20 an JP3 dient nur für interne Testzwecke und darf vom Anwender nicht gesetzt werden!

# 4.5 Jumperblockbelegung JP7

Durch das Setzen von Jumperbrücken an JP7 ist es möglich, die interne Versorgungsspannung Vcc (+5V) und die Masse (GND) des Rechners auf die D-Sub Buchse P1 zu legen.

# 4.6 Jumperblockbelegung JP9

Durch das Setzen von Jumperbrücken an JP9 ist es möglich, die interne Versorgungsspannung Vcc (+5V) und die Masse (GND) des Rechners auf den Pfostenstecker P9 zu legen.

# 5. Systemkomponenten

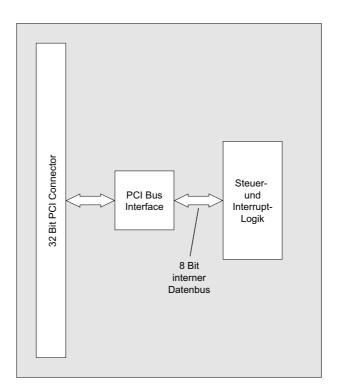

# 5.1 Blockschaltbild

# 5.2 Zugriff auf die Systemkomponenten

Der Zugriff auf die Hardware-Komponenten der ADIODA-PCI12 erfolgt durch das Lesen von bzw. Schreiben in Portadressen mit Hilfe von Library-Funktionen. Die für die ADIODA-PCI12 relevanten Portadressen ergeben sich abhängig von einer vom PCI-Bios vergebenen Basisadresse. Der Portzugriff auf die ADIODA-PCI12 erfolgt ausschließlich im Byte Zugriff (8Bit), Word und Doppel-Word Zugriffe können nicht verwendet werden. (Hinweise hierzu finden Sie im Kapitel Programmierung sowie in den Beispielprogrammen auf der mitgelieferten CD).

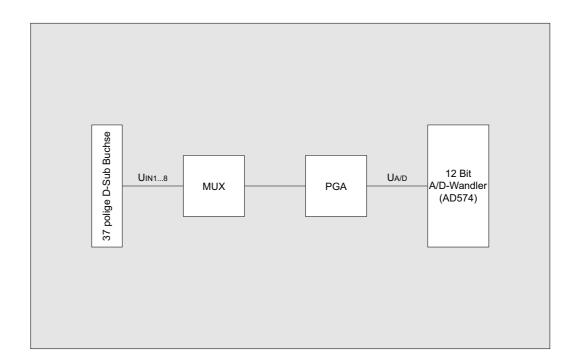

# 6. 8 A/D-Eingänge 12 Bit

Die ADIODA-PCI12<sub>LAP</sub> verfügt über 8 gemultiplexte massebezogene 12-Bit-A/D-Eingangskanäle mit programmierbarem Verstärker.

Der A/D-Eingangsbereich (0...10V, +/-5V, +/-10V) wird mittels Jumperstellung an JP1 festgelegt. Die weiteren Einstellungen (Multiplexer-Kanalauswahl, PGA-Verstärkungswahl und A/D-Betriebsart-Selektion) erfolgen rein softwaremäßig.

Die A/D-Wandlungen können entweder durch Softwaretriggerung, zeitlich definiert durch den Timerbaustein oder durch ein externes Signal ausgelöst werden. Die maximale Summenabtastrate beträgt 25 kHz.

Für die möglichen Eingangsspannungsbereiche ergeben sich folgende Jumperstellungen:

# Wichtiger Hinweis:

Eingangsspannungen außerhalb des eingestellten Eingangsspannungsbereiches sowie Jumperstellungen, die von den hier genannten abweichen, sind um Beschädigungen an der ADIODA-PCI12<sub>LAP</sub> auszuschließen, unbedingt zu vermeiden.

#### 6.1 A/D-Kontrollregister

Die ADIODA-PCI12<sub>LAP</sub> benützt die Portadressen BASISADRESSE + 00H bis einschließlich BASISADRESSE + 03H sowie die Adresse BASISA-DRESSE + 0EH (Adressparameterbezeichner ADCON1 bis ADCON5 in den Libraryfunktionen) zur Kontrolle des A/D-Wandlers, des Multiplexerbausteins sowie des programmierbaren Verstärkers. Je nachdem, ob in die jeweilige Portadresse geschrieben oder der Registerinhalt gelesen wird, ergibt sich folgende Bedeutung der Kontrollregister:

| Adressparame-<br>terbezeichner | Basisadresse+ | Register               | Schreiben        | Lesen         |

|--------------------------------|---------------|------------------------|------------------|---------------|

| ADCON1                         | 00H           | A/D-Kontrollregister 1 | 8-Bit-A/D-Start  | 8-Bit-MSB     |

| ADCON2                         | 01H           | A/D-Kontrollregister 2 | 12-Bit-A/D-Start | 4-Bit-LSB     |

| ADCON3                         | 02H           | A/D-Kontrollregister 3 | MUX-Kontrollbyte | Statusbyte    |

| ADCON4                         | 03H           | A/D-Kontrollregister 4 | PGA-Kontrollbyte | Int. FF Reset |

| ADCON5                         | 0EH           | A/D-Kontrollregister 5 | A/D-Modusbyte    |               |

Das Schreiben eines beliebigen Bytes in die Portadresse BASISADRES-SE + 01H (ADCON2) bzw. BASISADRESSE + 00H (ADCON1) löst eine 12-Bit-A/D-Wandlung (bzw. 8-Bit-A/D-Wandlung) aus. In diesen Fällen spricht man von softwaremäßiger Wandlungsauslösung oder Softwaretriggerung. Durch das Lesen eines Bytes von diesen Portadressen erhält man die höchstwertigen acht Bit bzw. die niederwertigsten vier Bit (mit nachfolgenden Nullen / nur bei 12-Bit-Wandlung) des Wandlungsergebnisses. Voraussetzung hierzu ist natürlich, dass im Moment des Lesebefehls gültige Daten vom A/D-Wandler bereitgestellt sind. Das Anliegen gültiger A/D-Daten kann man durch Lesen des "Status"-Bytes von der Portadresse BASISADRESSE + 02H (ADCON3) feststellen.

Das Schreiben eines Bytes in eine der Portadressen BASISADRESSE + 03H (ADCON3) und BASISADRESSE + 0EH (ADCON5) bestimmt die Funktion des Multiplexers, des programmierbaren Verstärkers bzw. des A/D-Wandlers selbst.

Nach dem Booten des Rechners befindet sich die ADIODA-PCI12<sub>LAP</sub> in folgendem Grundzustand:

A/D-Modus: Softwaretriggerung

Multiplexer: Kanal 1 selektiert

PGA: Verstärkung 1

Interrupt-Flipflop: zurückgesetzt

# 6.2 Multiplexer-Kanalauswahl

Die Auswahl eines der 8-A/D-Eingangskanäle erfolgt durch Schreiben eines "Multiplexer-Kontrollbytes" in die Portadresse BASISADRESSE + 02H (ADCON3).

Das Multiplexer-Kontrollbyte hat folgendes Format:

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|----|----|----|----|----|----|----|----|

| X  | Х  | Х  | K4 | K3 | K2 | K1 | K0 |

| X | X        | X | K4 | <b>K</b> 3 | K2 | <b>K</b> 1 | K0 | Kanal-Nr. |   |   |

|---|----------|---|----|------------|----|------------|----|-----------|---|---|

|   |          |   | 0  | 0          | 0  | 0          | 0  | 1         |   |   |

|   |          |   |    | 0          | 0  | 0          | 1  | 2         |   |   |

|   |          |   | 0  | 0          | 0  | 1          | 0  | 3         |   |   |

| h | aliahi   | ~ | 0  | 0          | 0  | 1          | 1  | 4         |   |   |

| D | beliebig |   | 0  | 0          | 1  | 0          | 0  | 5         |   |   |

|   |          |   |    |            | 0  | 0          | 1  | 0         | 1 | 6 |

|   |          |   |    | 0          | 1  | 1          | 0  | 7         |   |   |

|   |          |   | 0  | 0          | 1  | 1          | 1  | 8         |   |   |

KByte = Kanal-Nr. minus 1

Beispiel:

Auswahl von Kanal 5 --> KByte = 4 (dezimal) = 04 (hexadezimal)

# 6.3 PGA-Verstärkungswahl

Mit dem PGA-Kontrollbyte (Portadresse des PGA-Kontrollregisters = BA-SISADRESSE + 03H) wird der Verstärkungsfaktor des programmierbaren Verstärkers (PGA) selektiert. Der PGA der ADIODA-PCI12<sub>LAP</sub> ist wie folgt mit den Eingangskanälen sowie dem A/D-Wandler verbunden:

Die Eingangsspannung UA/D am Wandler ergibt sich wie folgt aus dem analogen Eingangssignal an einem der Kanäle 1...8 (selektiert mit dem Multiplexer-Kontrollbyte) und dem eingestellten Verstärkungsfaktor VPGA:

$$U_{A/D} = U_{IN} * V_{PGA}$$

(V<sub>PGA</sub> = 1,2,4,8,16)

#### Hinweis:

Es ist unbedingt sicherzustellen, dass die Eingangsspannung am Wandler (UA/D) im erlaubten Eingangsbereich (abhängig von der Jumperstellung JP1) liegt. Hierauf ist insbesondere bei Verwendung von unterschiedlichen Verstärkungsfaktoren für verschiedene Eingangskanäle zu achten!

Das PGA-Kontrollbyte hat folgendes Format:

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|----|----|----|----|----|----|----|----|

| Х  | Х  | Х  | Х  | Х  | P2 | P1 | P0 |

| Х | Х | Х      | Х | Х | P2 | P1 | P0 | Verstärkungs-<br>faktor |

|---|---|--------|---|---|----|----|----|-------------------------|

|   |   |        |   |   | 0  | 0  | 0  | 1                       |

|   |   |        |   |   | 0  | 0  | 1  | 2                       |

|   | b | eliebi | 9 |   | 0  | 1  | 0  | 4                       |

|   |   |        |   |   | 0  | 1  | 1  | 8                       |

|   |   |        |   |   | 1  | Х  | Х  | 16                      |

#### Beispiel:

Verstärkungsfaktor = 4

port(BASISADRESSE + \$3):= \$02;

outport(BASISADRESSE + \x03, \x02');

OUT BASISADRESSE + &H03,&H02

# 6.4 A/D-Betriebsarten (Modusbyte)

Der A/D-Block der ADIODA-PCI12<sub>LAP</sub> kann hinsichtlich A/D-Auflösung, Triggerung (=A/D-Wandlungsauslösung) und Interrupthandling in den folgenden verschiedenen Betriebsarten eingesetzt werden:

- --> A/D-Auflösung

- 1. 12-Bit-Auflösung

- 2. 8-Bit-Auflösung

- --> Triggerung (Wandlungsauslösung)

- 1. Softwaretriggerung

- 2. Hardwaretriggerung durch externes Signal

- 3. Hardwaretriggerung durch Timer-Signal OUT2

- --> Interrupthandling

- 1. keine Interruptauslösungen

- 2. Timer-Interrupt

- 3. Interrupt bei Wandlungsende (durch das Statussignal des A/D-Wandlers)

- 4. Interrupt durch externes Signal

Die Einstellung der Betriebsart erfolgt durch Schreiben eines Steuerbytes in die Portadresse BASISADRESSE + 0EH (ADCON5) des Modusregisters der ADIODA-PCI12<sub>LAP</sub>. Das Format des Modusbytes ist im folgenden Kapitel beschrieben.

## Modusbyte:

Das Modusbyte dient zur Programmierung der Art der Wandlungsauslösung (softwaremäßig, Timer-Auslösung bzw. durch externes Signal), der Wandlungsauflösung (8 bzw. 12 Bit) sowie der Interrupt-Quelle (STS-Signal vom A/D-Wandler, Timer Ausgangssignal bzw. externes Signal) bei Interruptanwendungen.

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|----|----|----|----|----|----|----|----|

| Х  | Х  | F5 | F4 | 13 | 12 | T1 | T0 |

| х     | Х    | F5                                                                | F4                        | 13                         | 12                       | T1                                                                                                                                                                                                                                                                 | то                              |                                                              |  |  |  |

|-------|------|-------------------------------------------------------------------|---------------------------|----------------------------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|--------------------------------------------------------------|--|--|--|

|       |      | Die Bits T0 und T1 legen die Art der Wandlungsauslösung fest      |                           |                            |                          |                                                                                                                                                                                                                                                                    |                                 |                                                              |  |  |  |

|       |      |                                                                   |                           |                            |                          | 0                                                                                                                                                                                                                                                                  | 0 0 Auslösung durch Software    |                                                              |  |  |  |

|       |      |                                                                   |                           |                            |                          | 0                                                                                                                                                                                                                                                                  | 1                               | Auslösung durch externes Signal                              |  |  |  |

|       |      |                                                                   |                           |                            |                          | 1                                                                                                                                                                                                                                                                  | 0                               | Auslösung durch Timer                                        |  |  |  |

|       |      | Die Bits I2 und I3 dienen zur Einstellung bei Interrupt-Auslösung |                           |                            |                          |                                                                                                                                                                                                                                                                    |                                 |                                                              |  |  |  |

|       |      |                                                                   |                           | 0                          | 0                        |                                                                                                                                                                                                                                                                    |                                 | kein Interrupt                                               |  |  |  |

|       |      |                                                                   |                           | 0                          | 1                        |                                                                                                                                                                                                                                                                    |                                 | Interrupt durch Timer                                        |  |  |  |

|       |      |                                                                   |                           | 1                          | 0                        |                                                                                                                                                                                                                                                                    |                                 | Interrupt durch STS-Signal                                   |  |  |  |

| belie | ebig |                                                                   |                           | 1                          | 1                        |                                                                                                                                                                                                                                                                    | Interrupt durch externes Signal |                                                              |  |  |  |

|       |      | War<br>Fall<br>durc                                               | ndlung<br>beliek<br>h ein | g als a<br>pig. B<br>exter | auch I<br>ei Wa<br>nes S | softwaremäßiger Wandlungsauslösung (sowohl bei 12Bit-<br>uch bei 8Bit-Wandlung) = 0 gesetzt werden. F5 ist in diesem<br>ii Wandlungsauslösung durch den Timer sowie bei Auslösung<br>ies Signal ist Bit F4 = 1 zu setzen. Bit F5 legt dann die Auflö-<br>ung fest. |                                 |                                                              |  |  |  |

|       |      | Х                                                                 | 0                         |                            |                          |                                                                                                                                                                                                                                                                    |                                 | Auslösung durch Software 12Bit und 8Bit                      |  |  |  |

|       |      | 0                                                                 | 1                         |                            |                          |                                                                                                                                                                                                                                                                    |                                 | Auslösung durch Timer od. externes Signal<br>Auflösung 12Bit |  |  |  |

|       |      | 1                                                                 | 1                         |                            |                          |                                                                                                                                                                                                                                                                    |                                 | Auslösung durch Timer od. externes Signal<br>Auflösung 8Bit  |  |  |  |

Grundsätzlich ist es möglich, die ADIODA-PCI12<sub>LAP</sub> je nach Aufgabenstellung in einer beliebigen Kombination aus den Einstellvarianten zu betreiben. Im folgenden werden die gebräuchlichsten Betriebsarten erläutert. Programmbeispiele finden Sie hierzu in der mitgelieferten Software.

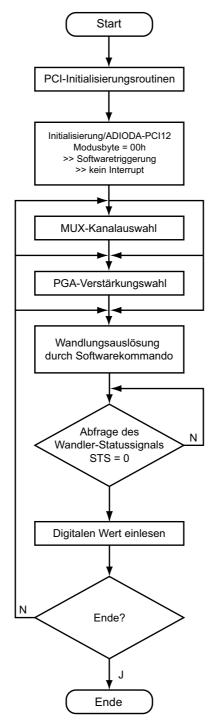

# 6.4.1 12-Bit/8-Bit-Wandlung (Softwaretriggerung/STS-Polling)

Die softwaremäßige Wandlungsauslösung mit Abfrage des Statussignales des A/D-Wandlers ist die einfachste Möglichkeit, A/D-Wandlungen mit der ADIODA-PCI12LAP auszuführen.

Nach der A/D-Initialisierung, der Kanalauswahl und der Auswahl des Verstärkungsfaktors erfolgt durch das Schreiben eines beliebigen Bytes in die Portadresse BASISADRESSE + 01H (ADCON2) bzw. BASISADRESSE + 00H (ADCON1) bei 8-Bit-Auflösung, der Start der 12-Bit-A/D-Wandlung.

Um sicherzustellen, dass der digitale Wert vom Wandlerausgang erst beim Anliegen gültiger Daten gelesen wird, muss das Statussignal des Wandlers, das während der Wandlung logisch "1" ist, abgefragt werden. Durch das Lesen von jeweils einem Byte von den Portadressen BASIS-ADRESSE + 00H (ADCON1) bzw. BASISADRESSE + 01H (ADCON2) erhält man die höchstwertigen 8 Bit bzw. die niederwertigsten 4 Bit des Wandlungsergebnisses.

Ablaufdiagramm/ 12-Bit-Wandlung (Softwaretriggerung/STS-Polling)

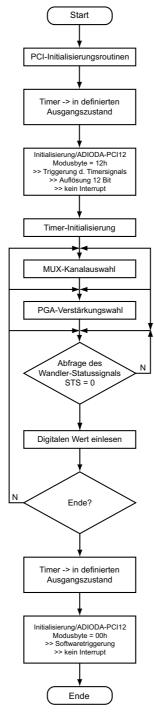

# 6.4.2 12-Bit-Wandlung (Timer-Auslösung/STS-Polling)

Mit Hilfe des 8254-Timerbausteines der ADIODA-PCI12<sub>LAP</sub> können auf einfache Weise zeitlich definierte "Abtastungen" des analogen Eingangssignals durchgeführt werden. Hierzu müssen die Jumper 1-2 bis einschließlich 17-18 am Jumperblock JP3 gesetzt sein. Die drei Zähler sind dann in Reihe geschaltet und erzeugen nach ihrer Initialisierung aus dem Oszillatorsignal das Triggersignal (=Timerausgangssignal OUT2) für den A/D-Wandler. Dieses Timersignal ist (bis zur Uminitialisierung des Timers) vom Programmablauf vollkommen unabhängig und deshalb zeitlich genau definiert.

Als Triggersignal für den A/D-Wandler ist ein negativer Impuls mit folgenden Voraussetzungen notwendig:

- 1. Die A/D-Wandlung wird bei der negativen Flanke des Triggersignales gestartet. OUT2 muss deshalb vor der Initialisierung des A/D-Wandlers auf "HIGH" liegen.

- 2. Die Zeitdauer des negativen Impulses darf nicht länger als die Wandlungszeit des jeweils verwendeten A/D-Wandlers sein. Empfehlenswert ist deshalb eine Impulsdauer von 5 µs.

Bis auf die A/D-Initialisierung und die Auslösung der Wandlungen durch den Timer ist diese Betriebsart vom Ablauf her mit der in Kapitel 6.4.1 geschilderten Betriebsweise identisch. Nach der A/D-Initialisierung, Auswahl des Verstärkungsfaktors und des Kanals erfolgt die Initialisierung des Timers und hierdurch der Start der A/D-Wandlungen.

Um sicherzustellen, dass der digitale Wert vom Wandlerausgang erst beim Anliegen gültiger Daten gelesen wird, muss das Statussignal des Wandlers, das während der Wandlung logisch "1" ist, abgefragt werden.

Durch das Lesen von jeweils einem Byte von den Portadressen BASIS-ADRESSE + 00H (ADCON1) bzw. BASISADRESSE + 01H (ADCON2) erhält man die höchstwertigen 8 Bit bzw. die niederwertigsten 4 Bit des Wandlungsergebnisses.

Bei Verwendung dieser Betriebsart muss zur Erzielung korrekter Meßergebnisse folgendes berücksichtigt werden:

Abhängig von der Frequenz des Triggersignales (= Abtastrate) steht nur ein bestimmter Zeitraum deltaT\_dat zwischen dem Ende der letzten Wandlung und dem Start der nächsten Wandlung für das Lesen des digitalen Wandlungswertes zur Verfügung.

Deshalb dürfen in dieser Zeit keine Programmunterbrechungen auftreten, die länger als die Zeit deltaT nop = deltaT dat - deltaT transfer ist.

deltaT\_transfer ist die vom Rechnertyp, der Programmiersprache und vom Programmieralgorithmus abhängige Zeit für das Abspeichern des digitalen Messwertes.

Ablaufdiagramm/ 12-Bit-Wandlung (Timer-Auslösung/STS-Polling)

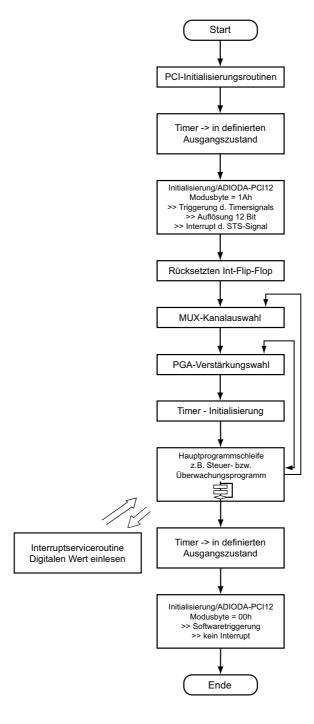

# 6.4.3 12-Bit-Wandlung (Timer-Auslösung/STS-Interrupt)

Die in Kapitel 6.4.2 geschilderte Betriebsart hat (insbesondere bei sehr niedrigen Abtastraten) den Nachteil, dass das ablaufende Programm nach dem Start der Wandlung ständig mit der Abfrage des Statussignales des A/D-Wandlers "beschäftigt" ist, und keinerlei andere Aufgaben übernehmen kann.

Sollen vom Hauptprogramm neben der Ermittlung von Analogwerten beispielsweise zusätzliche Steuer- oder Überwachungsaufgaben (z.B. mit Hilfe des 8255 I/O-Bausteins) übernommen werden, so ist die Betriebsart Timer/STS-Interrupt vorteilhaft.

Das Statussignal des A/D-Wandlers löst hierbei beim Ende der Wandlung automatisch einen Hardwareinterrupt aus. Das Einlesen der digitalen Wandlungswerte erfolgt dann innerhalb einer Interrupt-Serviceroutine. Die Wandlungsauslösungen erfolgen, wie bereits in Kapitel 6.4.1 geschildert, unabhängig vom Programmablauf durch das Timer-Ausgangssignal.

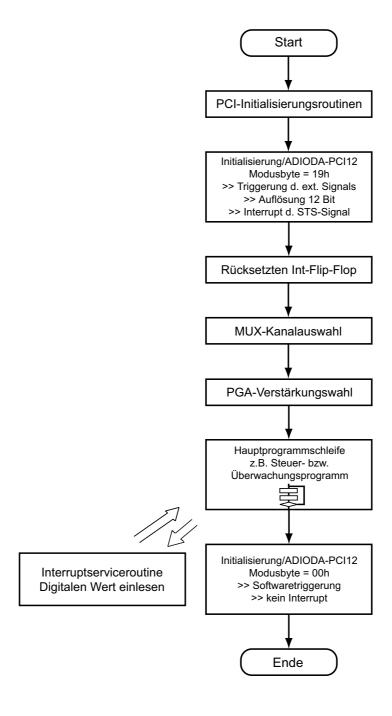

Ablaufdiagramm/ 12-Bit-Wandlung (Timer-Auslösung/STS-Interrupt)

#### 6.4.4

# 12-Bit-Wandlung (Auslösung durch externes Signal/STS-Interrupt)

Diese Betriebsart eignet sich für Anwendungen, in denen die A/D-Wandlungen durch ein externes Signal gesteuert werden sollen. Zur Wandlungsauslösung ist ein positiver Impuls an Pin 17 von P1 notwendig. Das Statussignal des A/D-Wandlers löst bei Wandlungsende automatisch einen Hardware-Interrupt aus. Das Einlesen der digitalen Wandlungswerte kann dann innerhalb einer Interrupt-Serviceroutine erfolgen.

#### Hinweis:

Als geeignetes Triggersignal empfehlen wir Ihnen einen positiven Impuls von 5 µs Dauer.

Die A/D-Wandlung wird mit der positiven Flanke des Triggersignals gestartet.

Für die Wandlungsauslösung durch ein externes Triggersignal muss der Platzhalter für RTEXT auf der Platine überbrückt werden.

Ablaufdiagramm/12-Bit-Wandlung (Externe Triggerung/STS-Interrupt)

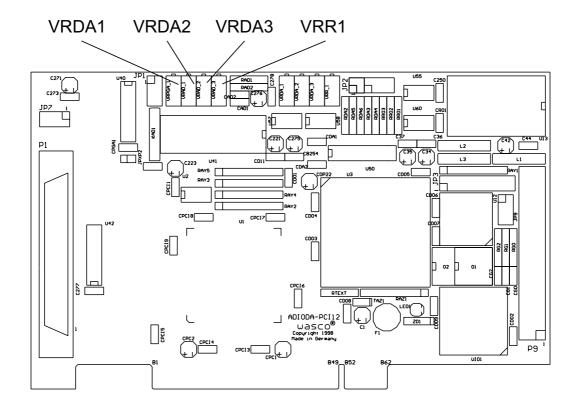

# 6.5 Abgleich A/D-Wandler und PGA

Die ADIODA-PCI12<sub>LAP</sub> ist standardmäßig auf den bipolaren Eingangsspannungsbereich +/-10V eingestellt und abgeglichen. Bei Änderungen der Grundeinstellung kann ein erneuter Abgleich des A/D-Systems notwendig sein. Aufgrund der Langzeitdriftdaten der Analog-Bauelemente und der Temperaturdrift ist darüberhinaus ein Abgleich der ADIODA-PCI12<sub>LAP</sub> unter Betriebsbedingungen zu empfehlen.

Den Abgleich des A/D-Systems sollten Sie mit dem Abgleichprogramm ADIPABGL.EXE durchführen oder wie folgt vorgehen:

## Abgleich des PGA:

- 1. Je nach Einstellung der ADIODA-PCI12LAP an Jumperblock JP1 Jumper 5-6 bzw. 7-8 ziehen.

- 2. Den momentan selektierten Eingangs-Kanal (Default-Kanal: Nr.1) mit AGND verbinden.

- 3. PGA-Verstärkung v = 16 einstellen.

- 4. Spannung an Pin 8 des Jumperblockes JP1 abgreifen.

- 5. PGA-Nullpunktoffset mit dem Trimm-Potentiometer VRPGA abgleichen (U<sub>Pin8</sub> = 0.00000V).

## Abgleich des A/D-Wandlers:

- 1. PGA-Verstärkung v = 1 setzen

- 2. Je nach gewünschtem Eingangsspannungsbereich Jumper JP1/5-6 bzw. 7-8 (Spannungsbereich) und Jumper JP1 /1-2 bzw. 3-4 (bipolare/unipolare Betriebsart) setzen.

- 3. Je nach Betriebsart, Nullpunktoffset des A/D-Wandlers mit Trimmer VRAD2 bzw. VRAD3 abgleichen.

Hierzu die unten angegebenen Spannungen an den momentan selektierten Eingangskanal legen und wiederholt den 12Bit-Wandlungswert lesen und abgleichen, bis der jeweilige Sollwert erreicht ist.

unipolare Betriebsart (0....10V):

Bei Anlegen einer Spannung von +1/2 LSB (=1.22mV) soll der digitale Wert zwischen 0000 0000 0000 und 0000 0000 0001 schwanken. --> Abgleichtrimmer VRAD3

bipolare Betriebsart:

Bei Anlegen einer Spannung von -Vfsr +1/2 LSB

soll der digitale Wert zwischen 0000 0000 0000 und 0000 0000 0001 schwanken. --> Abgleichtrimmer VRAD2

## 4. Abgleich des Endbereiches des A/D-Wandlers

Mit Spindeltrimmer VRAD1 auf den vom Eingangsspannungsbereich abhängigen Sollwert abgleichen.

unipolare Betriebsart (0....10V): Bei Anlegen einer Spannung von Vfsr -1 1/2 LSB (= 9.9963V) soll der digitale Wert zwischen 1111 1110 und 1111 1111 schwanken.

bipolare Betriebsart:

Bei Anlegen einer Spannung von Vfsr -1 1/2 LSB

soll der digitale Wert zwischen 1111 1111 1110 und 1111 1111 1111 schwanken.

# 7. 1 D/A-Ausgang 12 Bit

Die Interfacekarte ADIODA-PCI12<sub>LAP</sub> verfügt über einen analogen Ausgangskanal mit einer Auflösung von 12 Bit, der durch einen multiplizierenden 12Bit Digital/Analogwandler erreicht wird. Mittels Jumper ist die Auswahl einer Hauptreferenzspannung ( $V_{Ref0}$ ) aus vier verschiedenen intern erzeugten Spannungen möglich. Aus dieser gewählten  $V_{Ref0}$  wird die Referenzspannung  $V_{RefA}$  gewonnen, die werksmäßig auf einen festen Spannungswert abgeglichen, aber auch variabel von ~ 0,25 \*  $V_{Ref0}$  bis ~ <  $V_{Ref0}$  einstellbar ist. Durch die unterschiedlichen Referenzspannungen lassen sich verschiedene Ausgangsspannungen, unipolar von 0-10V und bipolar bis zu einem Endbereich von +/-10V erzeugen. Die Hauptreferenzspannung sowie die unipolare oder bipolare Betriebsart wird mittels Jumper JP2 eingestellt.

## 7.1 Auswahl der Betriebsart und der Hauptreferenzspannung

Durch Setzen zweier Jumper am Jumperblock JP2 können Sie die für Sie geeignete Hauptreferenzspannung  $V_{\text{Ref0}}$  sowie die Betriebsart auswählen. Standardmäßig wird vor der Auslieferung an JP2, Jumper 1-2 und Jumper 11-12 für den bipolaren Betrieb mit  $V_{\text{Ref0}}$  = 10V gesetzt.

Aus der Hauptreferenzspannung  $V_{\text{Ref0}}$  (über JP2 wählbar) ist mittels des Abgleichtrimmers VRR1 für  $V_{\text{RefA}}$  der Spannungsbereich 0,25 \*  $V_{\text{Ref0}}$  bis  $V_{\text{Ref0}} < V_{\text{Ref0}}$  einstellbar. Werksmäßig ist  $V_{\text{RefA}}$  für den Default-Bereich 10V auf  $V_{\text{RefA}} \sim 10V$  abgeglichen. Die Feineinstellung wird über VRDA1 vorgenommen. Der Nullpunktabgleich wird, wie in Kapitel 7.2 beschrieben, durchgeführt.

## 7.2 Abgleich des D/A-Kanals

Die ADIODA-PCI12<sub>LAP</sub> wird vor der Auslieferung für den Default-Bereich bipolar +/-10V, fein abgeglichen. Bei Verwendung eines Ausgangsspannungsbereichs der von der Standardeinstellung abweicht oder bei Umjumperung auf unipolare Betriebsart ist ein Feinabgleich durchzuführen. Zum Abgleich dient Ihnen das auf der beiliegenden Diskette abgelegte Abgleichprogramm ADIPABGL.EXE

Der Trimmer VRR1 ist zum Grobabgleich bestimmt. Mit dem Trimmer VRDA1 ist der Fein-Abgleich des Endbereichs möglich. Der Trimmer VRDA2 dient zum Nullpunktabgleich bei bipolarer Betriebsart, VRDA3 zum Nullpunktabgleich für den unipolaren Bereich.

## 7.3 Programmierung des D/A-Kanals

### 1. unipolarer Betrieb:

Der D/A-Wandler der ADIODA-PCI12<sub>LAP</sub> wandelt die an den digitalen Eingängen anliegende 12Bit-Information nach folgenden Beziehungen in einen analogen Ausgangsspannungswert:

(0000 0000 0000 ..... 1111 1111 1111 binär)

(0 ..... 4095 dezimal)

V<sub>fsr</sub> = maximaler Spannungswert

$1 LSB = V_{fsr}/4096$

$$n = V_{\text{OUT}}$$

$V_{\text{OUT}} = 0V + (n/4096) * V_{\text{fsr}}$

| Digitale<br>Eingänge | Dezimalwert | Vout<br>(Berechnung)    | Vout (Vfsr = 10 V)     |

|----------------------|-------------|-------------------------|------------------------|

| 1111 1111 1111       | 4095        | Vfsr * 4095/4096        | 9.9976 V               |

| 1000 0000 0000       | 2048        | Vfsr * 2048/4096        | 5.0000 V               |

| 0000 0000 0001       | 1           | Vfsr * 1/4096<br>(1LSB) | 0.00244 V =<br>2.44 mV |

| 0000 0000 0000       | 0           | 0 V                     | 0.0000 V               |

Der maximale Spannungswert  $V_{fsr}$  ergibt sich aus der durch die Abgleichtrimmer  $V_{RR1}$  und  $V_{RDA1}$  eingestellten Referenzspannung  $V_{RefA}$ .

## 2. bipolarer Betrieb:

Der D/A-Wandler der ADIODA-PCI12<sub>LAP</sub> wandelt die an den digitalen Eingängen anliegende 12Bit-Information nach folgenden Beziehungen in einen analogen Ausgangsspannungswert:

n = anliegender digitaler 12Bit-Wert

(0000 0000 0000 ..... 1111 1111 1111 binär)

(0 ..... 4095 dezimal)

V<sub>fsr</sub> = maximaler Spannungswert

$1 LSB = V_{fsr}/2048$

$$v_{OUT} + v_{f_{sr}}$$

$v_{OUT} = -v_{fsr} + (n/2048) * v_{fsr}$

| Digitale<br>Eingänge | Dezimalwert | Vout (Berechnung)        | Vout (Vfsr = 10 V) |

|----------------------|-------------|--------------------------|--------------------|

| 1111 1111 1111       | 4095        | -Vfsr + Vfsr * 4095/2048 | 9.9951 V           |

| 1000 0000 0000       | 2048        | -Vfsr + Vfsr * 2048/2048 | 0.0000 V           |

| 0000 0000 0001       | 1           | -Vfsr + Vfsr * 1/2048    | -9.9951 V          |

| 0000 0000 0000       | 0           | -Vfsr                    | -10.0000 V         |

Das Programmieren des D/A-Ausgangs mit dem 12Bit-Digitalwert erfolgt durch das Schreiben von einem LOW-Byte und einem HIGH-Halbbyte in die entsprechenden Portadressen des D/A-Kanals.

## Beispiel:

In der bipolaren Betriebsart (+/-10V) soll ein Spannungswert von +2.5 Volt am D/A-Kanal ausgegeben werden:

$$V_{OUT} + V_{fsr}$$

n =  $V_{fsr}$  \* 2048 = 2560 (dezimal) = A00 (hexadezimal)

# 8. 24 TTL Ein-/Ausgänge (8255)

Zur digitalen Ein-/Ausgabe ist auf der ADIODA-PCI12LAP ein Schnittstellen-Baustein vom Typ 8255 vorhanden. Der I/O-Baustein 8255 ist ein programmierbarer Mehrzweck-Ein-/Ausgabe-Baustein. Er hat 24 Ein-/Ausgabeanschlüsse, die in zwei Gruppen von je zwölf Anschlüssen getrennt programmierbar sind und im wesentlichen in drei Betriebsarten benutzt werden können. In der ersten Betriebsart (Betriebsart 0) kann jede Gruppe von zwölf Ein-/Ausgabeanschlüssen in Abschnitten von acht bzw. vier Anschlüssen als Eingang oder Ausgang programmiert werden. In der zweiten Betriebsart (Betriebsart 1) können acht Leitungen jeder Gruppe als Eingang oder Ausgang programmiert werden. Von den verbleibenden vier Anschlüssen werden drei für den Austausch von Quittungen und für Unterbrechungs-Steuersignale verwendet. Die dritte Betriebsart (Betriebsart 2) kann als Zweiweg-BUS-Betriebsart bezeichnet werden. Hier werden acht Anschlüsse für einen Zweiweg-BUS eingesetzt. Die fünf weiteren Anschlüsse, von denen einer zur anderen Gruppe gehört, werden in diesem Fall für den Quittungsaustausch benutzt. Außerdem ist das direkte Setzen und Rücksetzen einzelner Bits möglich.

# 9. 3 \* 16 Bit Zähler (Timer 8254)

Zur Generierung zeitgesteuerter Interruptauslösungen verfügt die ADI-ODA-PCI12 über eine Kombination aus 8254-Timerbaustein und Quarzoszillator. Alle Interruptanforderungen werden über die PCI-Bus-Leitung INTA an einen der Rechner-IRQs weitergeleitet. Die betreffende IRQ-Nummer wird vom PCI-PNP-Bios des Rechners selbständig vergeben.

Falls der Timer zur Generierung von zeitgesteuerten Interruptauslösungen benutzt werden soll, kann dies durch entsprechende Verbindungen am Jumperblock JP3 erfolgen. Hierzu müssen an JP3 die Jumperverbindungen 1-2 bis einschließlich 17-18 gesetzt werden. Durch entsprechende Programmierung der Zähler kann dann das Signal zur Interruptauslösung (Ausgang OUT2 von Zähler 2) erzeugt und an die Interruptlogik weitergeleitet werden. Unterbrechungsanforderungen werden bei Übergang von HIGH auf LOW-Pegel an OUT2 des Timer-Bausteins erzeugt.

# 10. Interrupt

### 10.1 Interrupt-Anforderungen

Interruptanforderungen können mit der ADIODA-PCI12<sub>LAP</sub> entweder zeitlich definiert durch den Timerbaustein, durch das Statussignal des A/D-Wandlers (bei Wandlungsende) oder durch ein externes Signal erzeugt werden. Alle Interruptanforderungen der ADIODA-PCI12 werden über die PCI-Bus-Leitung INT A an einen der Rechner-IRQs weitergeleitet. Die betreffende IRQ-Nummer wird vom PCI-PNP-Bios des Rechners bzw. durch das Betriebssystem vergeben. Die Auswahl der Interruptquelle und die interne Freigabe erfolgt durch das A/D + IRQ-Modusbyte (Kapitel 6.4).

Nach der Freigabe des vom PCI-Bios für die ADIODA-PCI12<sub>LAP</sub> vergebenen Rechner IRQs werden Interrupts abhängig von der programmierten Interruptquelle (nur eine IRQ-Betriebsart kann selektiert werden) wie folgt ausgelöst:

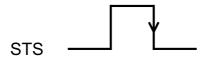

## 10.2 Interrupt durch Statussignal des A/D-Wandlers (STS)

Interrupt bei Wandlungsende (siehe auch Kapitel 6.4)

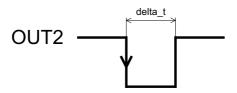

## 10.3 Interrupt durch Timersignal

Interrupt bei Übergang High ---> Low von OUT2 (siehe auch Kapitel 6.4) empfohlen: delta t = 5 µs

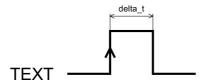

## 10.4 Interrupt durch externes Signal

Interrupt bei Übergang Low ---> High von externem Triggersignal (siehe auch Kapitel 6.4).

empfohlen: delta t < 5 µs

#### Hinweis:

Bei Verwendung eines externen Triggersignals muss RTEXT auf der Platine überbrückt sein!

Details zur Interrupt-Programmierung finden Sie in den Programmbeispielen auf der mitgelieferten CD!

In der Interruptservice-Routine kann die Plausibilität der IRQ-Anforderung durch die ADIODA-PCI12MCL durch das Lesen des Interrupt-Statusregisters (Test von Bit 2) überprüft werden:

Zur Feststellung muss das eingelesene Byte mit \$04 UND-Verknüpft werden.

---> IRQ falls das gelesene Byte "UND" \$04 = \$04

Das Rücksetzen der Interrupt-Anforderungen erfolgt kartenspezifisch durch das Lesen von Register ADCON4 (Rücksetzen des Interrupt-Flipflops) sowie rechnerspezifisch über die Register der Interrupt-Controller des PCs.

Details zur Interrupt-Programmierung finden Sie in den Programmbeispielen auf der mitgelieferten CD!

# 11. Programmierung unter DOS®

### 11.1 Programmierung der ADIODA-PCI12

In der beiliegenden Software finden Sie Bibliotheksfunktionen und Beispielprogramme zum Zugriff auf die ADIODA-PCI12 unter DOS®. Die Programmierung der Hardwarekomponenten der ADIODA-PCI12 erfolgt durch den Zugriff auf Portadressen, die sich abhängig von der vom PCI-Bios für die ADIODA-PCI12 vergebenen I/O-Basisadresse (und der LC-Basisadresse) ergeben. Mit Hilfe von Initialisierungsroutinen können sowohl die I/O-Basisadresse, die LC-Basisadresse als auch die direkten Portadressen der einzelnen Hardwarekomponenten festgestellt werden. Zusätzlich kann auf weitere Informationen wie IRQ-Nummer, Lokalisierung der Karte im Bussystem und Kartenversion zugegriffen werden. Sollten Sie mit einer Programmiersprache arbeiten, für die (noch) keine Bibliotheks-Funktionen verfügbar sind, können Sie mit Hilfe des Programms "WAD12SCA" (-> im Verzeichnis UTIL) die PCI-Parameter der ADIODA-PCI12 feststellen.

#### **PCI-Parameter:**

- I/O-Basisadresse

- IRQ-Nummer

- LC-Basisadresse

- Bus-Nummer

- Device-Nummer

- Funktionsnummer

- ADIODA-Version

### **PCI-Identifikation:**

| Device-ID           | = | \$9050 |

|---------------------|---|--------|

| Vendor-ID           | = | \$10B5 |

| Subsystem-Vendor-ID | = | \$10B5 |

| Subsystem-ID        | = | \$1152 |

## 11.2 Zuordnung der Portadressen

Die Portadressen der einzelnen Hardware-Komponenten ergeben sich abhängig von der I/O-Basisadresse (BA) und der LC-Basisadresse (LC) wie folgt:

| Port/<br>Register            | BA + Offset<br>(hexadezimal) | Befehls-<br>funktion |

|------------------------------|------------------------------|----------------------|

| A/D + IRQ-Kontrollregister 1 | BA + \$0                     | lesen/schreiben      |

| A/D + IRQ-Kontrollregister 2 | BA + \$1                     | lesen/schreiben      |

| A/D + IRQ-Kontrollregister 3 | BA + \$2                     | lesen/schreiben      |

| A/D + IRQ-Kontrollregister 4 | BA + \$3                     | lesen/schreiber      |

| 3255-I/O-Port A              | BA + 4                       | lesen/schreiben      |

| 8255-I/O-Port B              | BA + 5                       | lesen/schreiben      |

| 8255-I/O-Port C              | BA + 6                       | lesen/schreiben      |

| 8255-I/O-Kontrollregister    | BA + 7                       | schreiben            |

| 3254-Timer 0                 | BA + 8                       | lesen/schreiber      |

| 3254-Timer 1                 | BA + 9                       | lesen/schreiber      |

| 8254-Timer 2                 | BA + \$A                     | lesen/schreiber      |

| 3254-Timer-Kontrollregister  | BA + \$B                     | lesen/schreiber      |

| D/A-Low-Byte                 | BA + \$C                     | schreiben            |

| D/A-High-Byte                | BA + \$D                     | schreiben            |

| A/D + IRQ-Kontrollregister 5 | BA + \$E                     | schreiben            |

| nterrupt-Statusregister      | LC + \$4C                    | lesen                |

# 12. Programmierung unter Windows®

### 12.1 Programmierung der ADIODA-PCI12

Für die Anwendung der Karte unter Windows® ist es notwendig, einen speziellen Treiber zu installieren, der den Portzugriff auf die Karte ermöglicht.

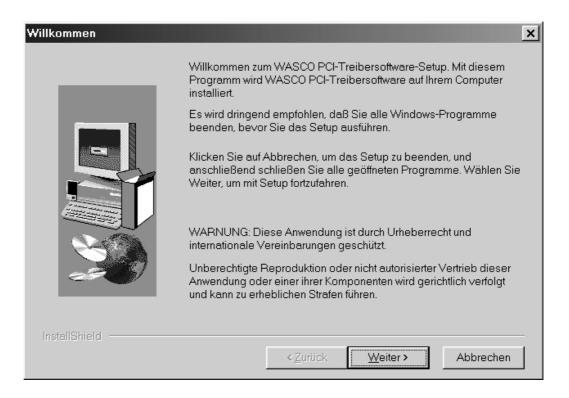

### 12.2 Installation der Windows® Treiber

Zur Installation des Windows<sup>®</sup> Treibers führen Sie bitte die Datei "Setup. Exe" im Ordner Treiber, auf der mitgelieferten CD aus und folgen Sie den Installationsanweisungen.

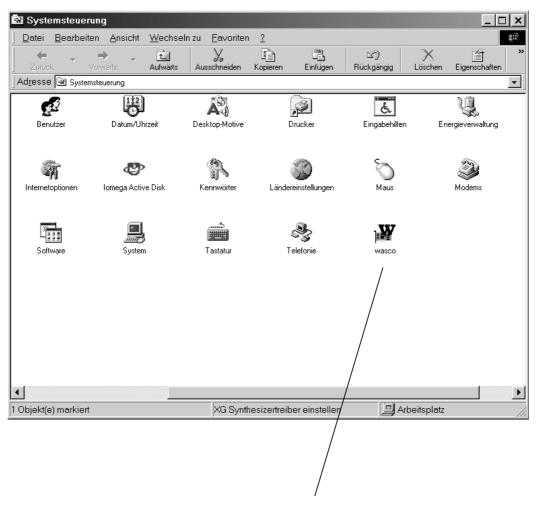

Wurde die Treibersoftware vollständig installiert, finden Sie in der Systemsteuerung Ihres Rechners ein Icon zur Lokalisierung aller im System vorhandenen **wasco**® PCI-Karten.

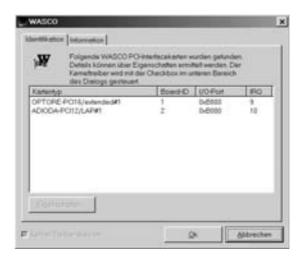

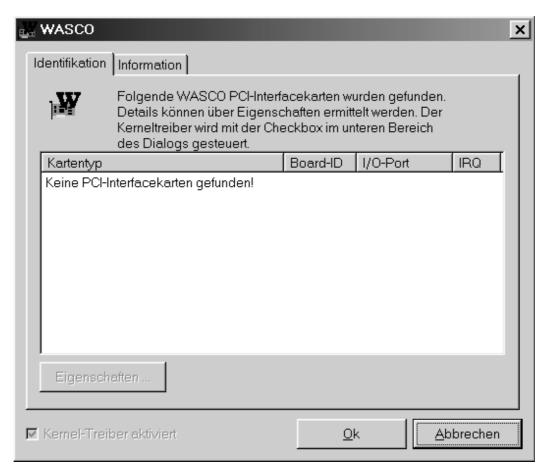

Starten Sie die Kartenabfrage durch einen Doppelklick auf das "wasco®" Icon. Folgendes Fenster erscheint: (Als Beispiel wurden hier eine OPTO-RE-PCI16 und eine ADIODA-PCI12 verwendet)!

Wurde Ihre Karte im System erkannt, wird der Kartenname, Board ID, I/O-Adresse sowie die mögliche Interruptnummer für die jeweilige Karte in diesem Fenster angezeigt. Desweiteren kann über den Button "Information" die Treiber-Version sowie der Standort der Treiberdatei abgefragt werden.

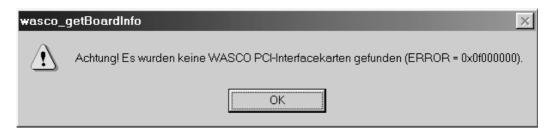

Wurde Ihre Karte im System nicht erkannt, werden folgende Fehlermeldungen angezeigt:

Informieren Sie sich im Kapitel Fehlersuche über die möglichen Ursachen!

# 13. Zubehör

## 13.1 Passendes wasco®-Zubehör

| Anschlussteile                    | EDV-Nr.  |

|-----------------------------------|----------|

| DS37R100 Anschlussleitung         | A-199802 |

| DS37R100DS37 Verbindungsleitung   | A-202200 |

| DS37R200DS37 Verbindungsleitung   | A-202400 |

| DS37R500DS37 Verbindungsleitung   | A-202800 |

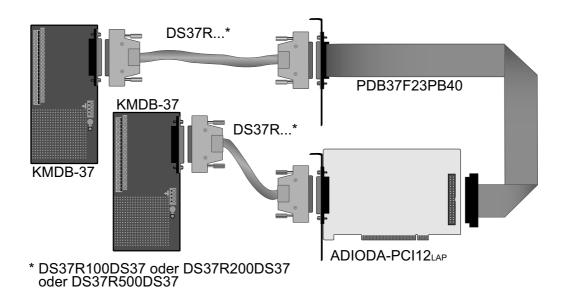

| KMDB-37 Klemm-Modul               | A-2046   |

| PDB37F23PB40 Steckerverlegungsset | A-497500 |

# 13.2 Anschlusstechnik (Anwendungsbeispiele)

# 13.3 Einzelkomponenten zur Eigenkonfektionierung

| Anschlussleitung                                    | EDV-Nr. |

|-----------------------------------------------------|---------|

| D-Sub-Stecker 37 pol. für Lötanschluss              | A-5506  |

| D-Sub-Haube 37 pol. Stecker (Lötanschluss)          | A-5586  |

| D-Sub-Stecker 37 pol. für Flachbandleitung          | A-5526  |

| D-Sub-Buchse 37 pol. für Flachbandleitung           | A-5566  |

| Slotblech mit Ausschnitt für 37 pol. Stecker/Buchse | A-5774  |

| Pfostenbuchse 40 pol. für Flachbandleitung          | A-5642  |

| Flachbandleitung 37 pol.                            | A-5718  |

| Flachbandleitung 40 pol.                            | A-5720  |

## 14. Fehlersuche

Nachfolgend finden Sie eine kurze Zusammenstellung der häufigsten, bekannten Fehlerursachen, die während der Inbetriebnahme oder während der Arbeit mit der ADIODA-PCI12 auftauchen können. Prüfen Sie bitte zunächst folgende Punkte, bevor Sie mit Ihrem Händler Kontakt aufnehmen.

- Sitzt die ADIODA-PCI12 richtig in der Steckverbindung?

- 2. Sind alle Kabelverbindungen in Ordnung?

- 3. Hat die Sicherung (F1) der ADIODA-PCI12 angesprochen?

- 4. Wurde die Karte im System richtig erkannt? Prüfen Sie hierzu alle Einstellungen in Ihrem Rechner oder wenden Sie sich an Ihren Systemadministrator. (Da es sich hierbei um Einstellungen im BIOS des Rechners handelt, können wir hier nicht näher darauf eingehen und verweisen hierzu auf Ihr Systemhandbuch)!

- 5. Wurde die neueste Treiberversion des **wasco**® Treibers installiert?

Updates finden Sie unter: http://www.messcomp.com

http://www.wasco.de

# 15. Technische Daten

A/D-Eingänge

Kanäle: 8 Eingänge single-ended

Auflösung: 8 Bit oder 12 Bit per Software einstellbar

A/D-Wandlerbaustein: ADS574 mit Sample and Hold

Multiplexerbaustein: MAX354CPE

Eingangsspannungs-

bereiche: bipolar: +/-5V, +/-10V

unipolar: 0....10V

Eingangsspannungs-

faktoren: 1, 2, 4, 8, 16 per Software wählbar

Wandlungsauslösung: softwaremäßig, über Timer oder ext. Signal

Summenabtastrate: max. 25KHz

Wandlungszeit des

Wandlers: 25µs Genauigkeit des Wandlers: +/- 1LSB

Datentransfer: Pollingbetrieb, interruptgesteuert

D/A-Ausgang

Kanäle: 1 Ausgang

Auflösung: 12 Bit

D/A-Baustein: DAC7541

Linearität: +/- 1LSB

Ausgangsspannungs-

bereiche: unipolar: 2.5V, 5V, 7.5V, 10V

bipolar: +/-2.5V, +/-5V,

+/-7.5V, +/-10V

Ausgangsstrom: +/-5 mA max. Einschwingzeit: 70µs max.

**Referenzspannung** Referenzspannungsquelle: AD584

Digitale Ein-/Ausgabe

Baustein: 8255

Kanäle: 24, TTL-Kompatibel

Port A und Port B in 8Bit-Gruppen Port C in eine 8Bit-Gruppe oder in zwei 4Bit-Gruppen als Ein- oder Ausgänge programmierbar

Belastbarkeit: loh -0,4mA 2,7V min.

IoL +2,5mA 0,4V max.

**Timer**

Baustein: 8254 (3 \* 16Bit Abwärtszähler)

Zählfrequenz: max. 8 MHz

Zeitabhängige Interruptauslösungen mittels Takt vom Quarzoszillator

**Quarzoszillator** 4 MHz

**Anschlussstecker** 1 \* 37polige D-Sub Buchse

2 \* 40poliger Pfostenstecker

**Bussystem** 32Bit PCI-Bus

(interner Datenbus 8 Bit)

**Stromverbrauch** +5V typ. 750mA

# 16. Produkthaftungsgesetz

### Hinweise zur Produkthaftung

Das Produkthaftungsgesetz (ProdHaftG) regelt die Haftung des Herstellers für Schäden, die durch Fehler eines Produktes verursacht werden.

Die Verpflichtung zu Schadenersatz kann schon gegeben sein, wenn ein Produkt aufgrund der Form der Darbietung bei einem nichtgewerblichen Endverbraucher eine tatsächlich nicht vorhandene Vorstellung über die Sicherheit des Produktes erweckt, aber auch wenn damit zu rechnen ist, dass der Endverbraucher nicht die erforderlichen Vorschriften über die Sicherheit beachtet, die beim Umgang mit diesem Produkt einzuhalten wären.

Es muss daher stets nachweisbar sein, dass der nichtgewerbliche Endverbraucher mit den Sicherheitsregeln vertraut gemacht wurde.

Bitte weisen Sie daher im Interesse der Sicherheit Ihre nichtgewerblichen Abnehmer stets auf Folgendes hin:

#### Sicherheitsvorschriften

Beim Umgang mit Produkten, die mit elektrischer Spannung in Berührung kommen, müssen die gültigen VDE-Vorschriften beachtet werden.

Besonders sei auf folgende Vorschriften hingewiesen: VDE0100; VDE0550/0551; VDE0700; VDE0711; VDE0860. Sie erhalten VDE-Vorschriften beim vde-Verlag GmbH, Bismarckstraße 33. 10625 Berlin.

- \* Vor Öffnen eines Gerätes den Netzstecker ziehen oder sicherstellen, dass das Gerät stromlos ist.

- \* Bauteile, Baugruppen oder Geräte dürfen nur in Betrieb genommen werden, wenn sie vorher in ein berührungssicheres Gehäuse eingebaut wurden. Während des Einbaus müssen sie stromlos sein.

- \* Werkzeuge dürfen an Geräten, Bauteilen oder Baugruppen nur benutzt werden, wenn sichergestellt ist, dass die Geräte von der Versorgungsspannung getrennt sind und elektrische Ladungen, die in im Gerät befindlichen Bauteilen gespeichert sind, vorher entladen wurden.

- \* Spannungsführende Kabel oder Leitungen, mit denen das Gerät, das Bauteil oder die Baugruppe verbunden sind, müssen stets auf Isolationsfehler oder Bruchstellen untersucht werden. Bei Feststellen eines Fehlers in der Zuleitung muss das Gerät unverzüglich aus dem Betrieb genommen werden, bis die defekte Leitung ausgewechselt worden ist.

- \* Bei Einsatz von Bauelementen oder Baugruppen muss stets auf die strikte Einhaltung der in der zugehörigen Beschreibung genannten Kenndaten für elektrische Größen hingewiesen werden.

- \* Wenn aus den vorgelegten Beschreibungen für den nichtgewerblichen Endverbraucher nicht eindeutig hervorgeht, welche elektrischen Kennwerte für ein Bauteil gelten, so muss stets ein Fachmann um Auskunft ersucht werden

Im Übrigen unterliegt die Einhaltung von Bau und Sicherheitsvorschriften aller Art (VDE, TÜV, Berufsgenossenschaften usw.) dem Anwender/Käufer.

# 17. EG-Konformitätserklärung

Für das folgende Erzeugnis

### ADIODA-PCI12LAP EDV-Nummer A-403400

wird hiermit bestätigt, dass es den Anforderungen der betreffenden EG-Richtlinien entspricht. Bei Nichteinhaltung der im Handbuch angegebenen Vorschriften zum bestimmungsgemäßen Betrieb des Produktes verliert diese Erklärung Ihre Gültigkeit.

EN 5502 Klasse B

IEC 801-2

IEC 801-3

IEC 801-4

EN 50082-1

EN 60555-2

EN 60555-3

Diese Erklärung wird verantwortlich für den Hersteller

Messcomp Datentechnik GmbH Neudecker Str. 11 83512 Wasserburg

abgegeben durch

Dipl.Ing.(FH) Hans Schnellhammer (Geschäftsführer)

J. S. S. S. S. Wasserburg, 23.05.2006

## Referenzsystem-Bestimmungsgemäßer Betrieb

Die PC-Erweiterungskarte ist ein nicht selbständig betreibbares Gerät, dessen CE-Konformität nur bei gleichzeitiger Verwendung von zusätzlichen Computerkomponenten beurteilt werden kann. Die Angaben zur CE-Konformität beziehen sich deshalb ausschließlich auf den bestimmungsgemäßen Einsatz der PC-Erweiterungskarte in folgendem Referenzsystem:

| Vero IMRAK 3400             | 804-530061C<br>802-563424J<br>802-561589J                                |

|-----------------------------|--------------------------------------------------------------------------|

| Vero PC-Gehäuse             | 145-010108L                                                              |

| Zusatzelektronik            | 519-112111C                                                              |

| GA-586HX                    | PIV 1.55                                                                 |

| auf Motherboard             |                                                                          |

| TEAC                        | FD-235HF                                                                 |

| Advantech                   | PCA-6443                                                                 |

| ADIODA-PCI12 <sub>LAP</sub> | A-403400                                                                 |

|                             | Vero PC-Gehäuse Zusatzelektronik GA-586HX auf Motherboard TEAC Advantech |